EGS3 Hardware Interface Description

Figures

8

EGS3_HD_v01.000a Page 7 of 117 2009-08-12

Confidential / Released

Figures

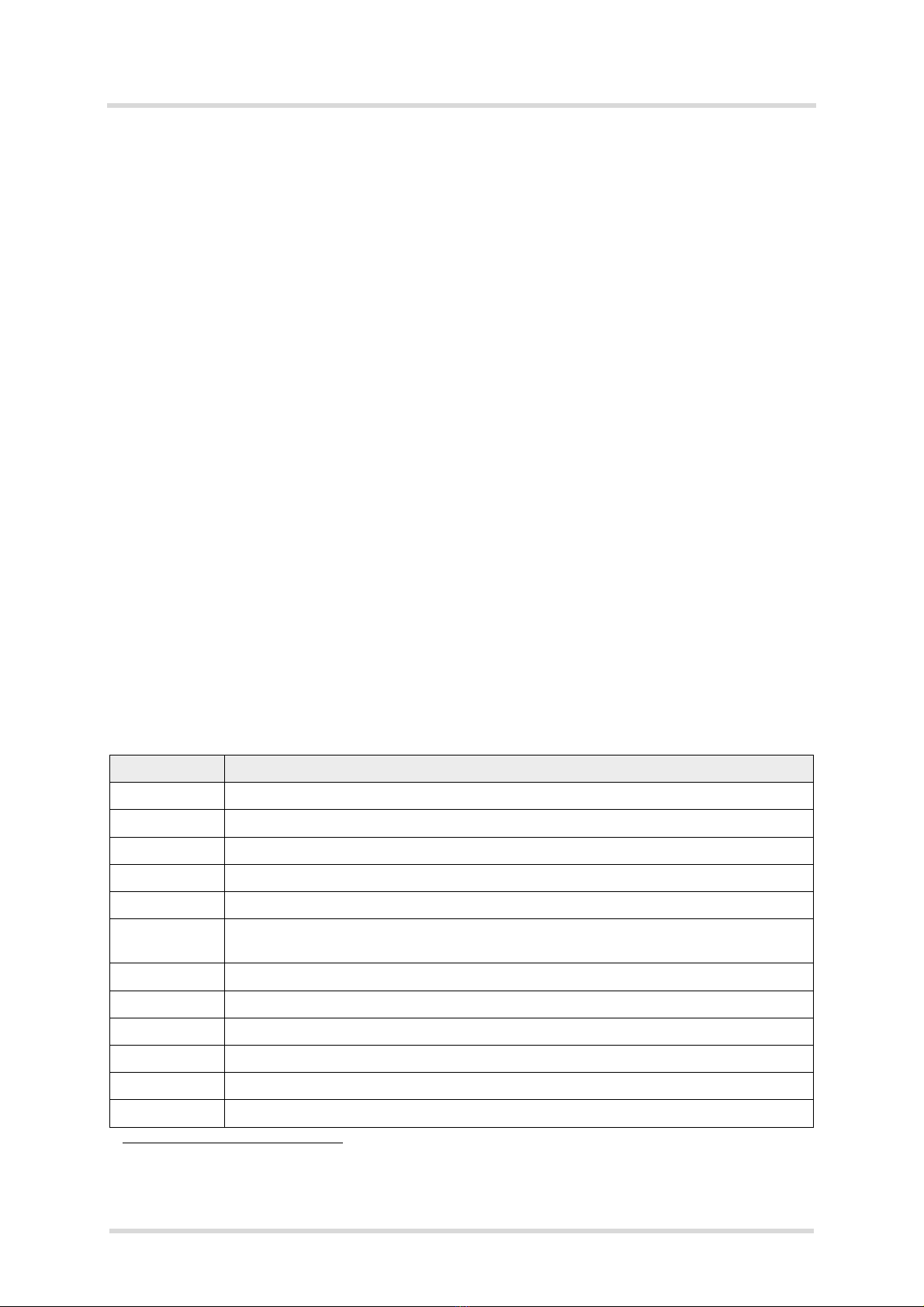

Figure 1: EGS3 system overview.................................................................................. 21

Figure 2: EGS3 block diagram ...................................................................................... 22

Figure 3: Power supply limits during transmit burst....................................................... 25

Figure 4: Position of reference points BATT+and GND ................................................ 26

Figure 5: Powerup with operating voltage at BATT+ applied before activating IGT...... 28

Figure 6: Powerup with IGT held low before switching on operating voltage at BATT+ 29

Figure 7: Timing of IGT if used as ON/OFF switch ....................................................... 30

Figure 8: Signal states during turn-off procedure.......................................................... 35

Figure 9: Battery pack circuit diagram........................................................................... 42

Figure 10: Power saving and paging............................................................................... 47

Figure 11: Timing of CTSx signal (if CFUN= 7)............................................................... 48

Figure 12: Timing of RTSx signal (if CFUN = 9).............................................................. 48

Figure 13: Serial interface ASC0..................................................................................... 51

Figure 14: Serial interface ASC1..................................................................................... 53

Figure 15: USB circuit ..................................................................................................... 54

Figure 16: I2C interface connected to VCC of application ............................................... 55

Figure 17: I2C interface connected to VEXT line of EGS3 .............................................. 55

Figure 18: SPI interface................................................................................................... 56

Figure 19: Characteristics of SPI modes......................................................................... 57

Figure 20: Audio block diagram....................................................................................... 58

Figure 21: Single ended microphone input...................................................................... 60

Figure 22: Differential microphone input ......................................................................... 61

Figure 23: Line input configuration with OpAmp ............................................................. 62

Figure 24: Differential loudspeaker configuration............................................................ 63

Figure 25: Master PCM interface Application.................................................................. 65

Figure 26: Short Frame PCM timing................................................................................ 65

Figure 27: Long Frame PCM timing ................................................................................ 66

Figure 28: Slave PCM interface application .................................................................... 67

Figure 29: Slave PCM Timing, Short Frame selected..................................................... 67

Figure 30: Slave PCM Timing, Long Frame selected...................................................... 67

Figure 31: SYNC signal during transmit burst................................................................. 68

Figure 32: LED Circuit (Example).................................................................................... 69

Figure 33: Incoming voice/fax/data call........................................................................... 70

Figure 34: URC transmission .......................................................................................... 70

Figure 35: Antenna pads................................................................................................. 71

Figure 36: 4 layer PCB stack for EGS3 interface board.................................................. 72

Figure 37: RF line on interface board. All dimensions are given in mm .......................... 74

Figure 38: Numbering plan for connecting pads (bottom view)....................................... 79

Figure 39: Audio programming model............................................................................. 92

Figure 40: EGS3– top view ............................................................................................. 99

Figure 41: Dimensions of EGS3 (all dimensions in mm)............................................... 100

Figure 42: Land pattern (bottom view) .......................................................................... 101

Figure 43: Recommended stencil design (bottom view) ............................................... 102

Figure 44: Reflow Profile............................................................................................... 103

Figure 45: Carrier tape .................................................................................................. 106

Figure 46: Reel direction ............................................................................................... 106

Figure 47: Barcode label on tape reel ........................................................................... 107

Figure 48: Moisture barrier bag (MBB) with imprint....................................................... 108

Figure 49: Moisture Sensitivity Label ............................................................................ 109

Figure 50: Humidity Indicator Card - HIC ...................................................................... 110